# **Image Signal Processor IP Core**

Released new product SHSA-01001 core with minimum functions for image processing.

SHSA-01 series

#### **Overview**

# **Compact ISP IP core**

- Compatible with Bayer filters on image sensors

- Implementable on both ASIC and FPGA

- Input/output I/F conforms to AMBA ※1

- Maximum image size: 4K x 2K pixels

- Supports RGB, YCbCr formats (No sensor correction)

- Equipped with the following functions

- Sensor correction : Black level correction, Demosaic, Color correction

- Automatic correction : AWB(Auto White Balance), AE(Auto Exposure)\*2

- Image correction : Tone curve correction、Gamma correction、Color space conversion

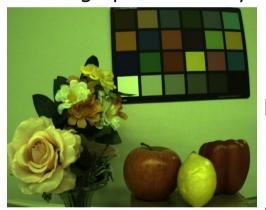

### ■ Image processed by SHSA-01001 ×3

Figure 1. Raw Image \*\*4

Figure 2. After Sensor correction

Figure 3. After Automatic Correction \*5

Figure 4. After Image Correction \*5

- X1 AMBA(Advanced Microcontroller Bus Architecture): ARM's on-chip bus standard.

- \*2 This IP only performs photometry, and requires separate control of the image sensor, etc.

- \*3 These are images output by implementing SHSA-01001 in FPGA.

- \*4 For comparison with color images, only demosaic processing is performed.

- ※5 Each correction includes all previous processing.

### **SHSA-01001 Specification**

|                     | FPGA (Cyclone® V ※1)                                 | ASIC (@28nm)   |

|---------------------|------------------------------------------------------|----------------|

| Gate Count          | 7,500 (ALMs) %2                                      | 210 (KGate) %2 |

| RAMs                | 73 (M10Ks) %2                                        | 550 (Kbit) %2  |

| DSPs                | 27                                                   | -              |

| Frame rate          | 40 fps %3                                            |                |

| Pixel rate          | 1 Pixel/CLK                                          |                |

| Image bit depth     | 12 bit %4                                            |                |

| Interfaces          | CPU I/F : AMBA3 APB<br>Image I/F : AMBA4 AXI4-Stream |                |

| Input color format  | RAW(Bayer)、RGB、YCbCr 4:4:4 %5                        |                |

| Output color format | RGB、YCbCr 4:4:4 %5                                   |                |

- \*1 Intel, the Intel logo, and other Intel names and logos are trademarks of Intel Corporation or its subsidiaries.

- X2 The value is for the maximum image size of 4096x2160.

- $\frak{3}$  It is the value when the image size is 1920x1080 and the clock frequency is 100MHz.

(100MHz: 4K 10fps, VGA 300fps)

Frame rate(fps) = Clock frequency (Hz) / Image pixel count (pixel)

- %4 If it is 12bit or less, it will be possible to input.

## **Applications**

- Security camera

- Monitoring camera

- Appearance inspection camera

etc.

In addition, it is also possible to support to the image input system.

#### **Customization**

IP core customization according to customer needs is available.

- Processing capacity

- IP core peripheral circuit design

- Gate amount reduction

http://www.shikino.co.jp/eng E-mail: ip\_sales@shikino.co.jp

#### ■Osaka Design Center

Shin-Osaka Nishiura Bldg 6F, 7-38, Nishimiyahara 2-chome, Yodogawa-ku, Osaka, 532-0004, Japan Phone :+81-6-6150-7730 FAX :+81-6-6150-7739